#### 23 March 2016 — Berkeley CA

### Neuromorphic Chips: Combining Analog Computation with Digital Communication

Kwabena Boahen Bioengineering and Electrical Engineering (by courtesy) Stanford University

## Acknowledgments

**Students** Ben Benjamin Alex Neckar Sam Fok Samir Menon Tatiana Engel Nick Oza John Aguayo Eric Kauderer Ashok Cutkosky Alumni (Recent) Peiran Gao Nick Steinmetz John Arthur Paul Merolla Rodrigo Alvarez

**Collaborators** Stanford Krishna Shenoy Tirin Moore Oussama Khatib Waterloo Chris Eliasmith Terry Stewart Cornell Rajit Manohar Ned Bingham Funding NIH Pioneer, TR01 **ONR: C. Baatar**

#### Analog VLSI and Neural Systems

Carver Mead

### "Listen to the technology and find out what it is telling you."

– Carver Mead, 1999

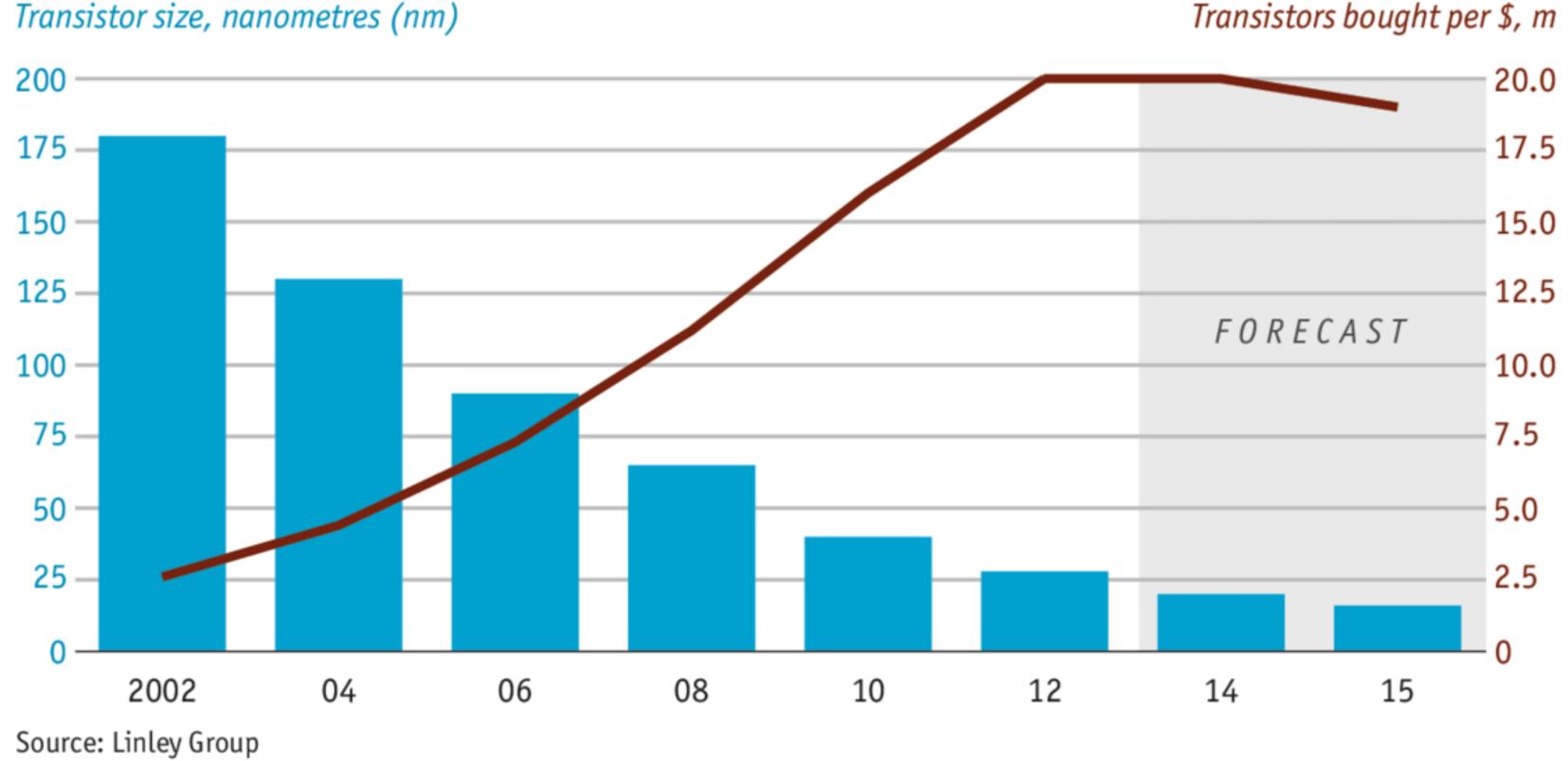

## It's getting really hard to shrink transistors

#### A persevering prediction

Number of transistors in CPU\* Log scale

Source: Intel

#### MOORE'S LAW DEFINED 1010 10<sup>8</sup> 106 104 10<sup>2</sup> 2000 10 14 1960 70 80 90

\*Central processing unit

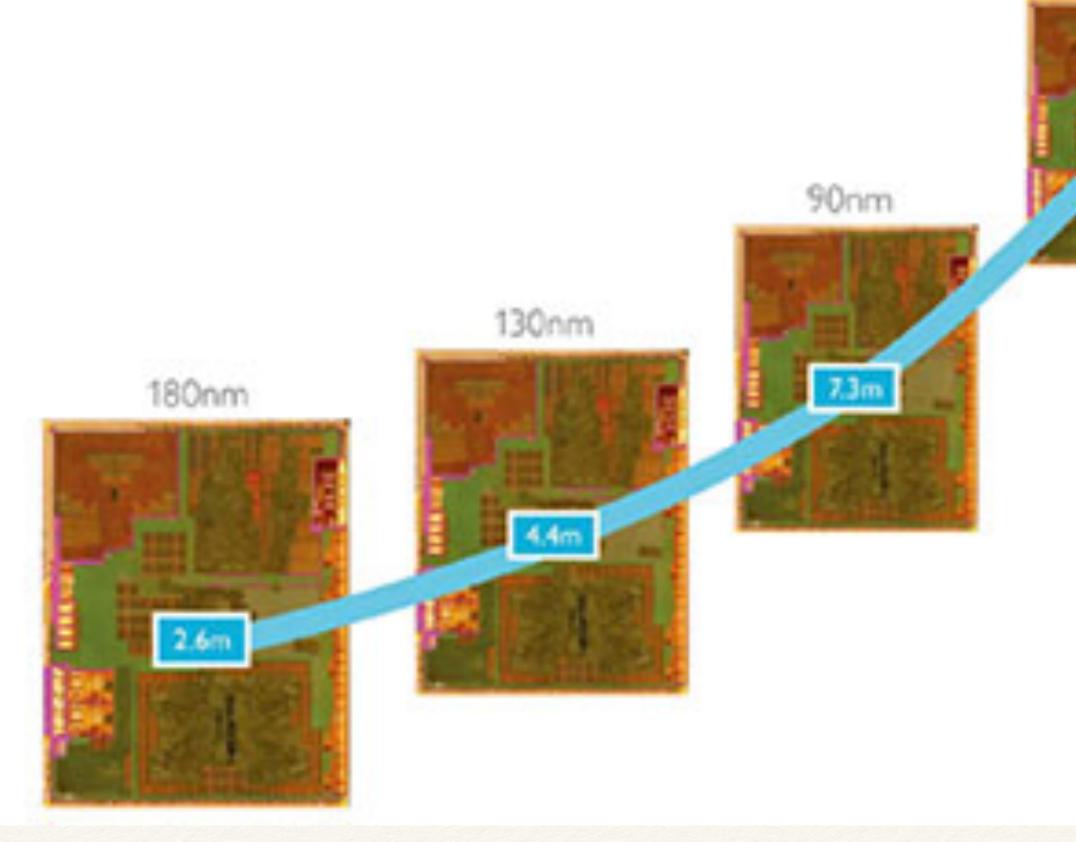

#### Shrinking chips

Number and length of transistors bought per \$

Transistor size, nanometres (nm)

The Economist 2015

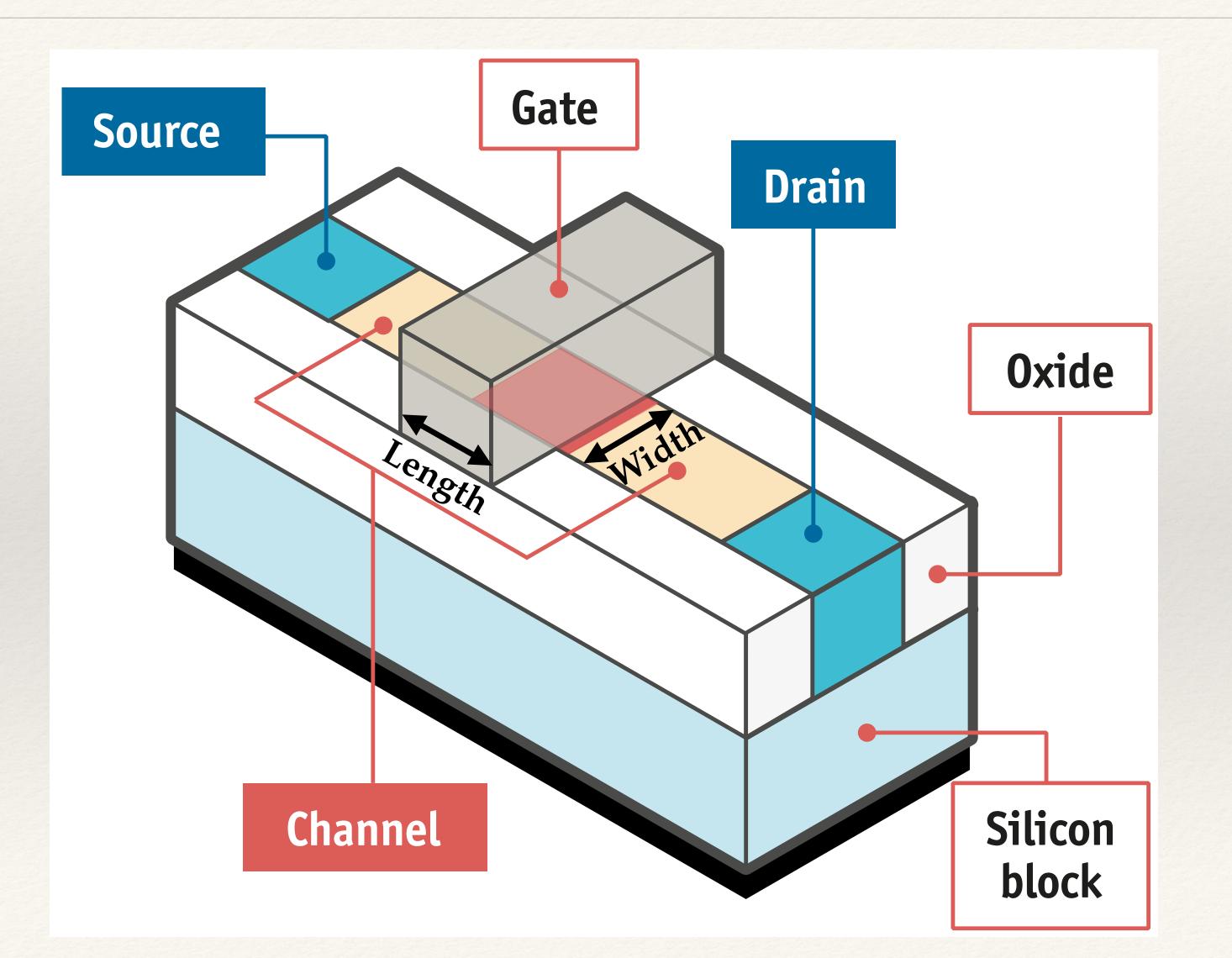

## The MOS Transistor

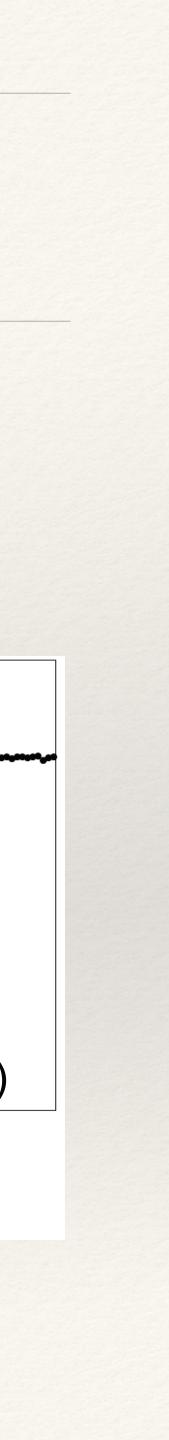

The Economist 2016

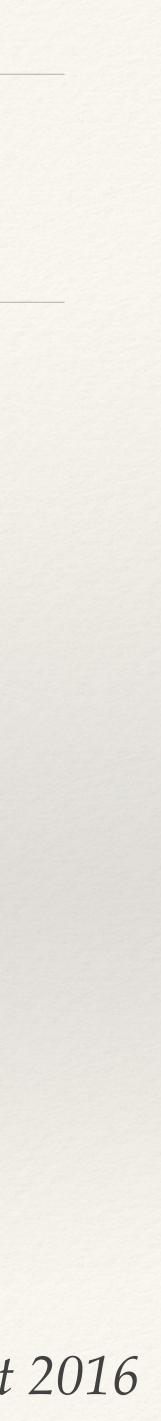

Watanabe et al 2014

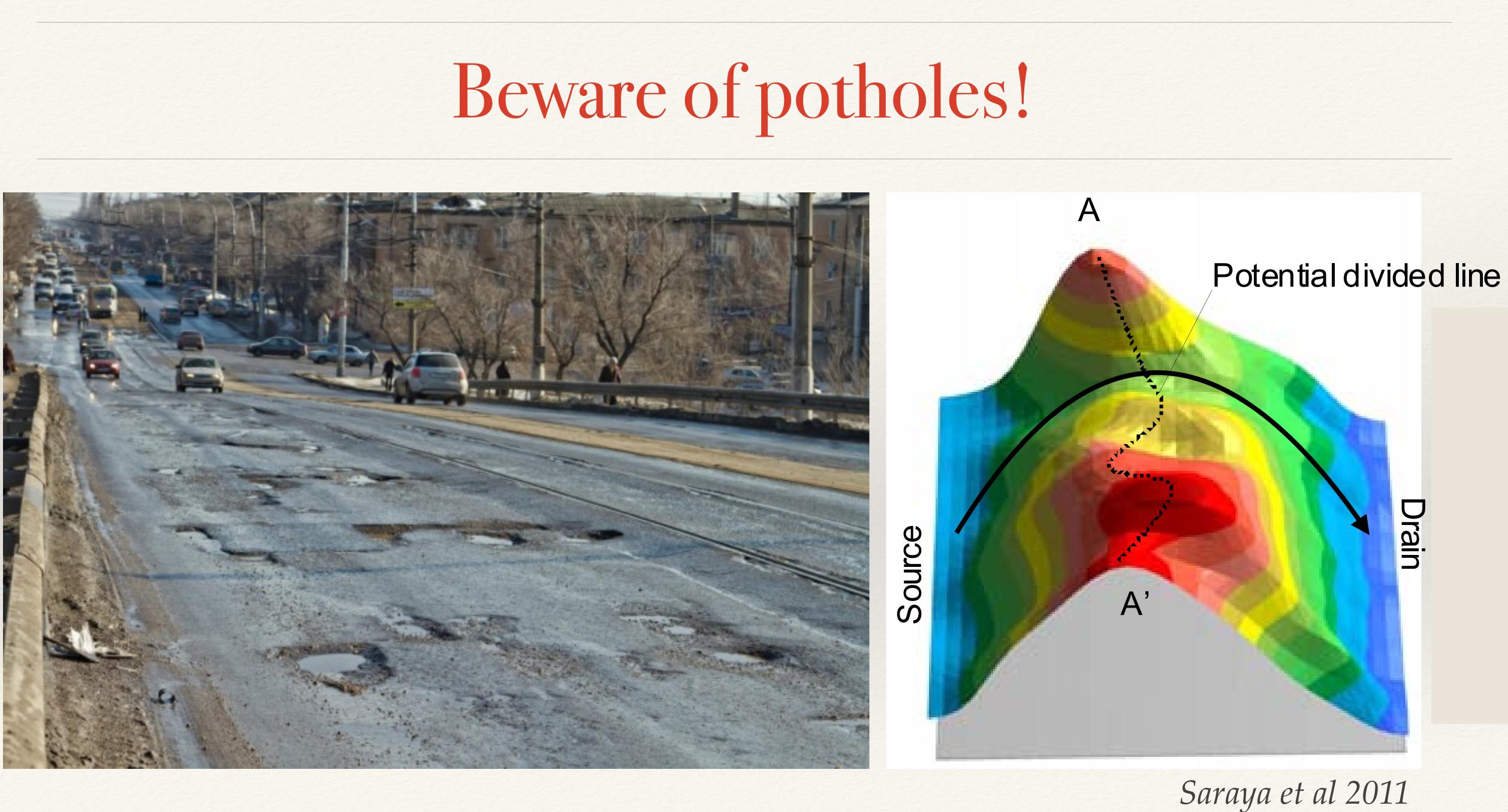

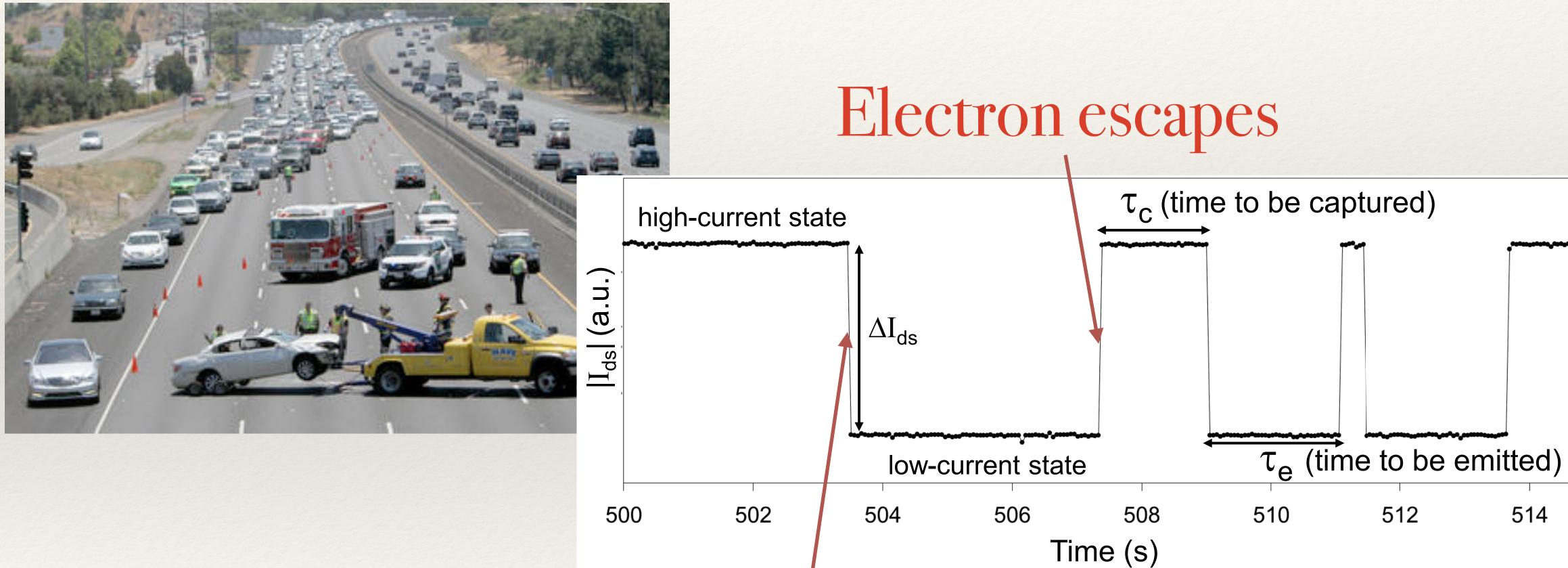

## Accidents occur!

## Electron trapped

#### The Economist 2016

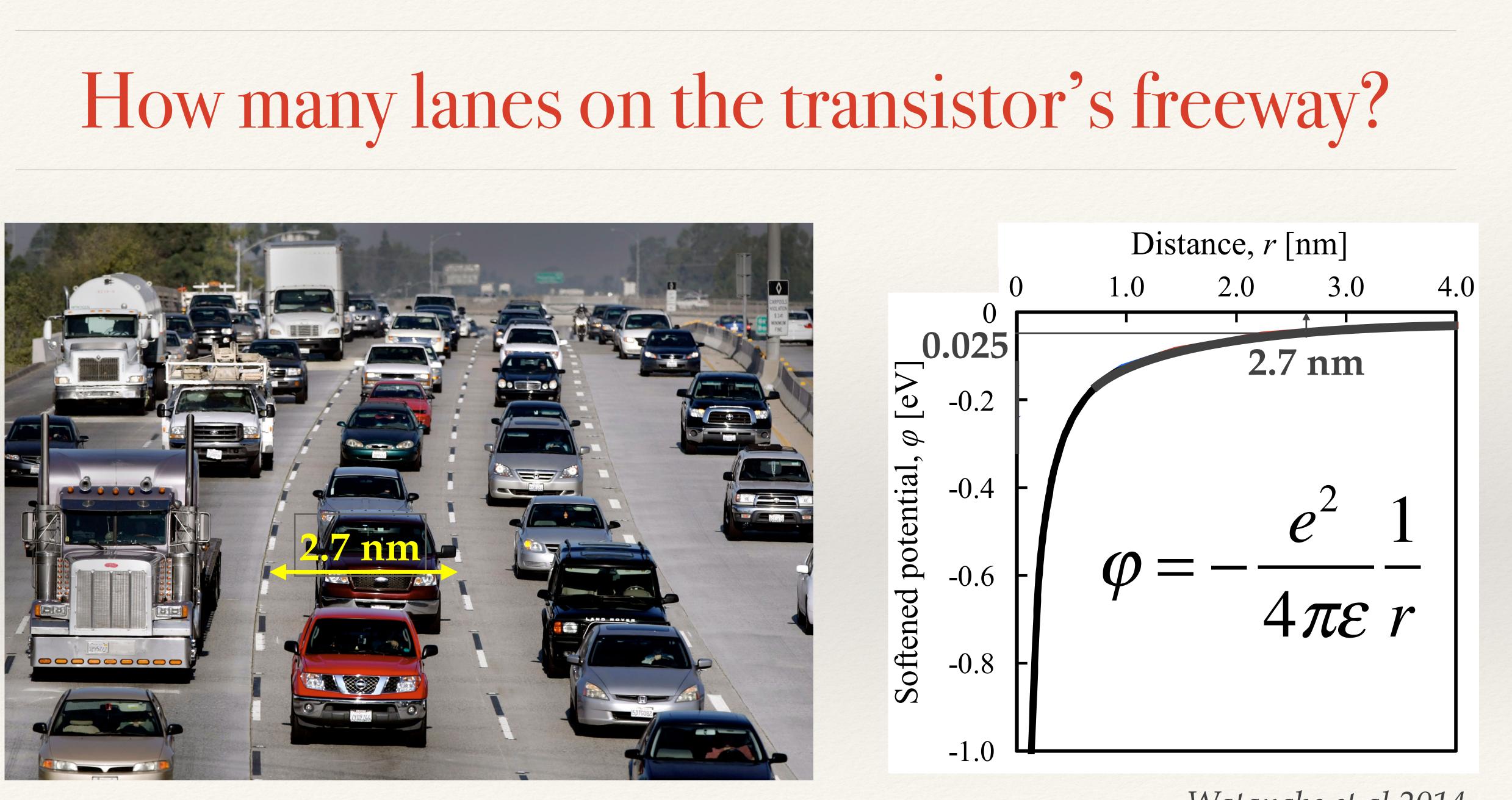

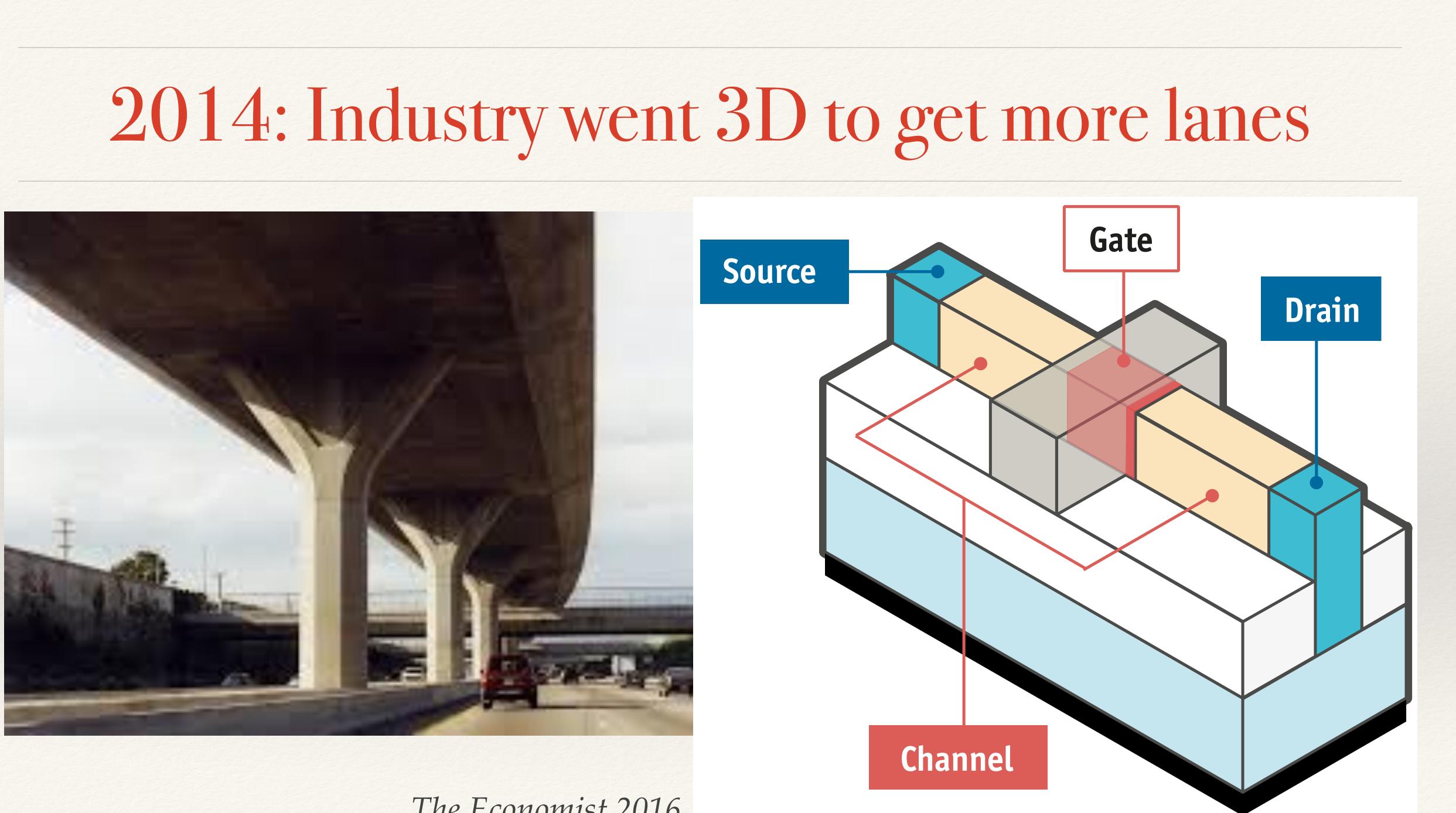

## Intel's 28nm FinFET: 30 lanes (13+4+13)

Average Fin pitch: 60 nm

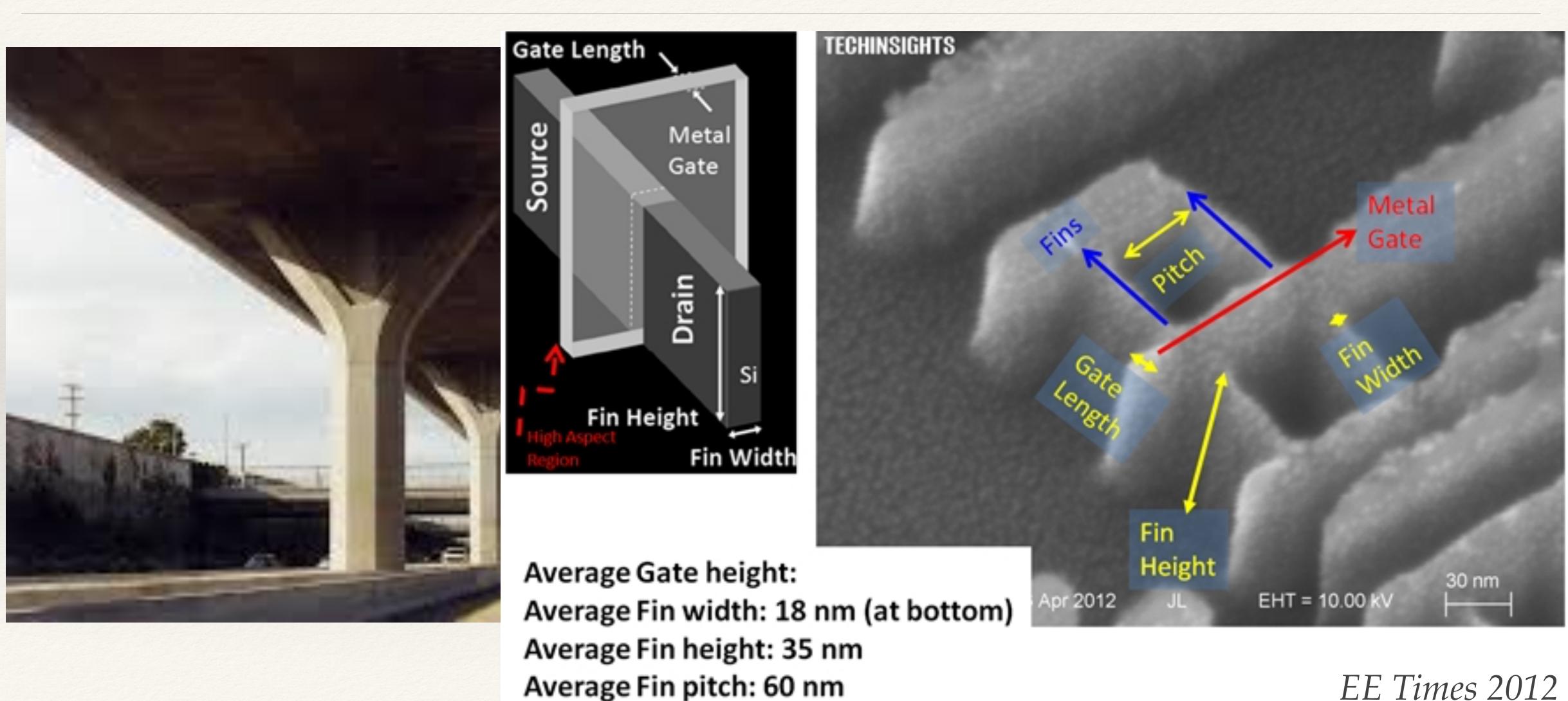

### 28nm: Optimal Balance of Cost and Power for 2015 Devices

Shrinking chips

Number and length of transistors bought per \$

- Mid-range devices are highly sensitive to cost

- 28nm provides the most transistors per dollar

ARM 2014

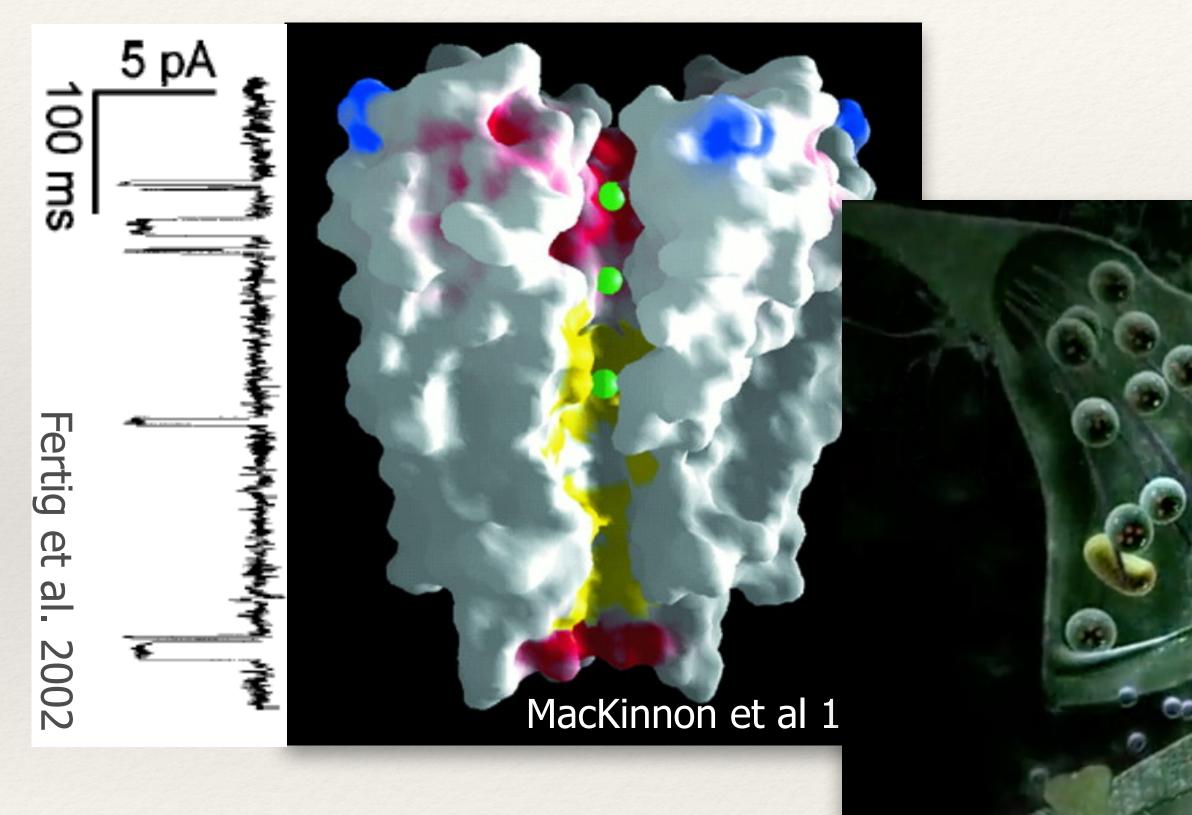

## Brains operate fine with single-lane ion-channels

#### 20 ion-channels

#### 2000 ion-channels

## JOHN VON NEUMANN THE COMPUTER AND THE BRAIN

"The most immediate observation regarding the nervous system is that its functioning is *prima facie* digital."

– John von Neumann 1957

## JOHN VON NEUMANN THE COMPUTER AND THE BRAIN

"Thus all the complexities referred to here may be irrelevant, but they may also endow the system with a (partial) analog character, or a 'mixed' character."

– John von Neumann 1957

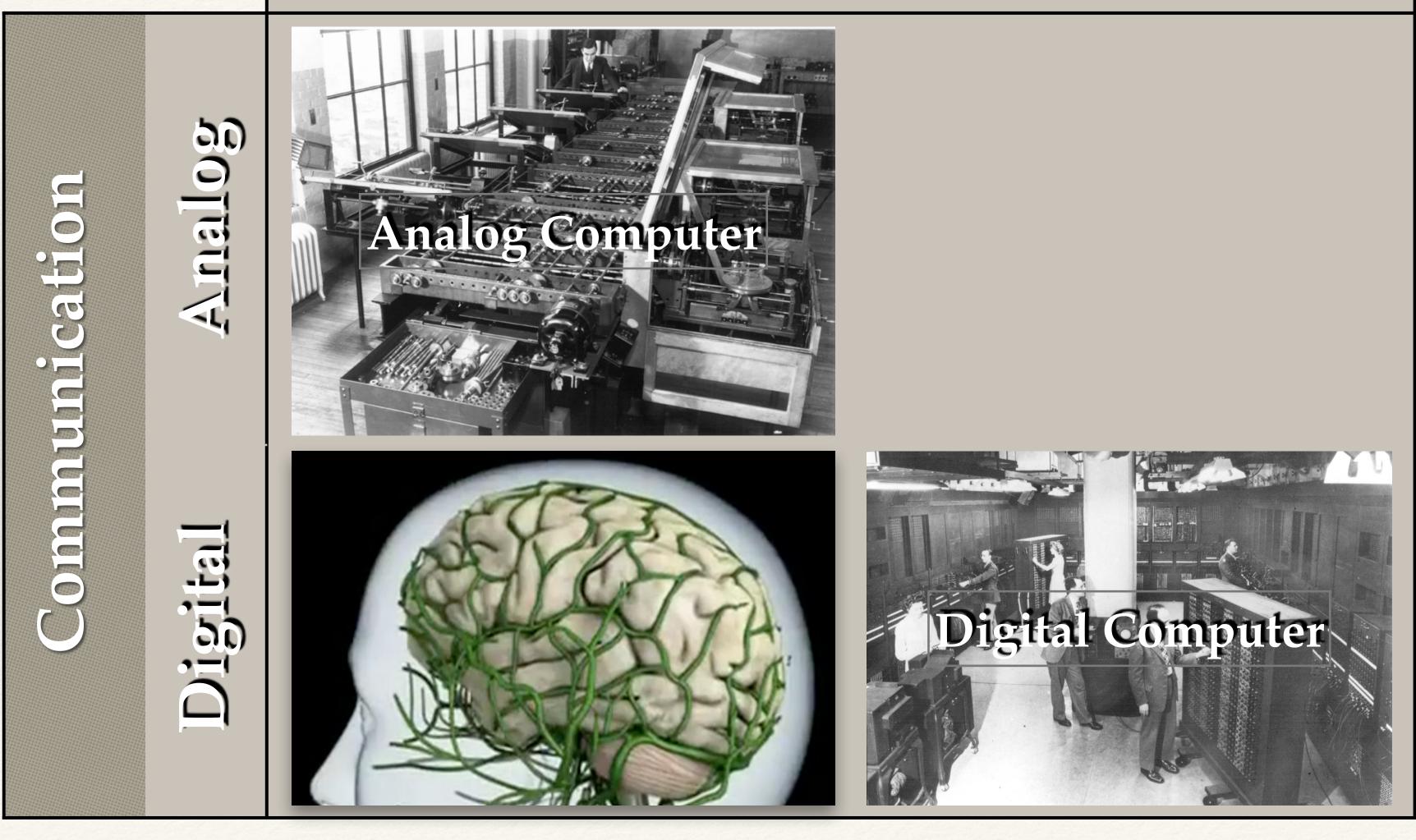

### Computation

### Digital

## Difference between Digital and Analog

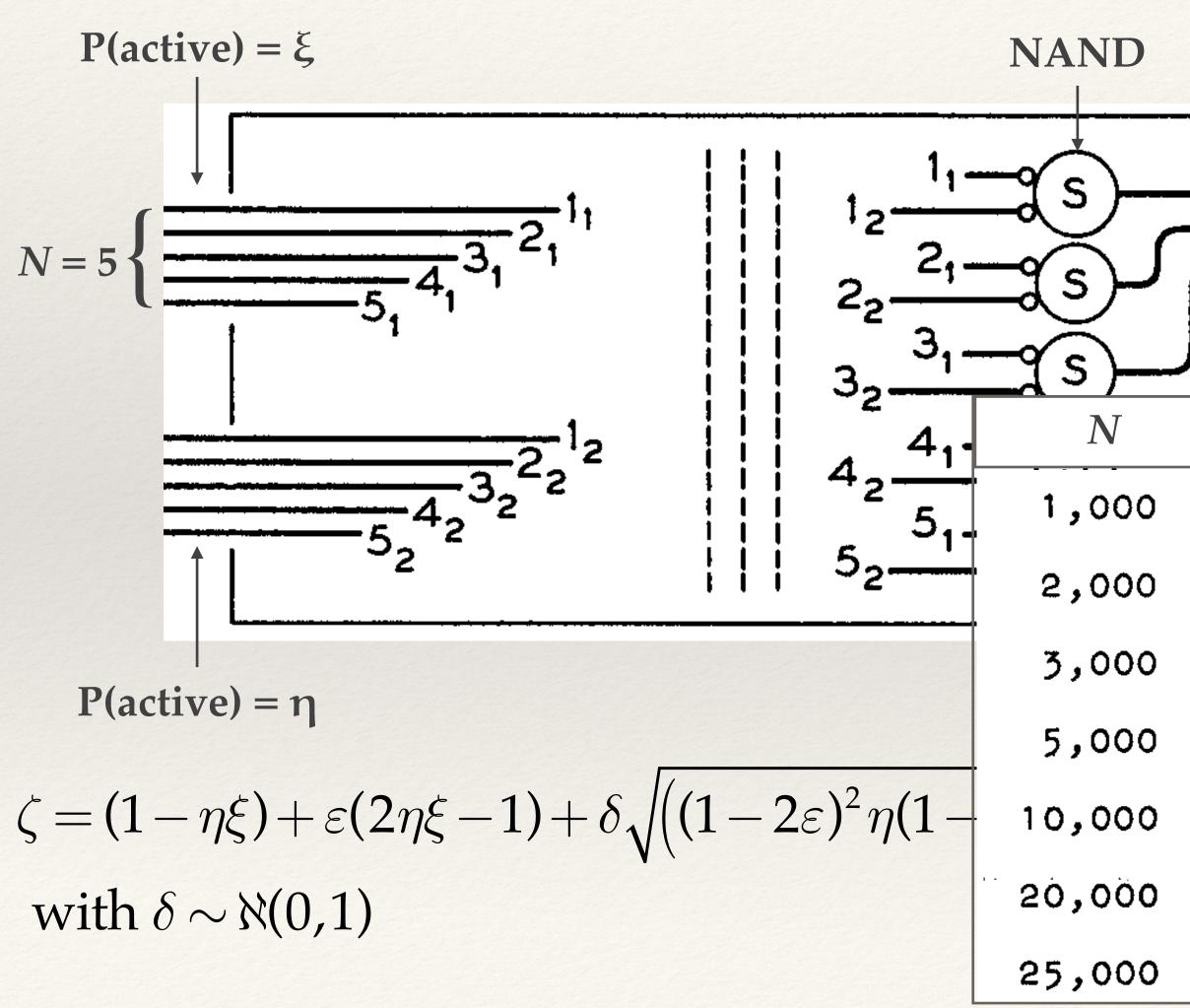

## Robust Digital Computation: N-way Redundancy

|   | $P(active) = \zeta$                              | * Binary code:<br>$\zeta > 0.97 \Rightarrow bit = 1$               |

|---|--------------------------------------------------|--------------------------------------------------------------------|

|   |                                                  | $\zeta < 0.03 \Rightarrow bit = 0$                                 |

| ſ |                                                  | othw $\Rightarrow$ error                                           |

|   | P(error)                                         | * For $\varepsilon > 1.07 \times 10^{-2}$ , increasing             |

|   | $2.7 \times 10^{-2}$                             | N doesn't help                                                     |

|   | $2.6 \times 10^{-3}$                             | * For $\varepsilon = 5 \times 10^{-3}$ :                           |

|   | $2.5 \times 10^{-4}$                             |                                                                    |

|   | $4 \times 10^{-6}$                               | $P(\text{error}) = \frac{6.4}{\sqrt{N}} 10^{-\frac{8.6N}{10,000}}$ |

|   | $1.6 \times 10^{-10}$<br>2.8 × 10 <sup>-19</sup> | $\sqrt{N}$                                                         |

|   | 2.8 × 10 <sup>-1.9</sup>                         |                                                                    |

|   | $1.2 \times 10^{-23}$                            | von Neumann                                                        |

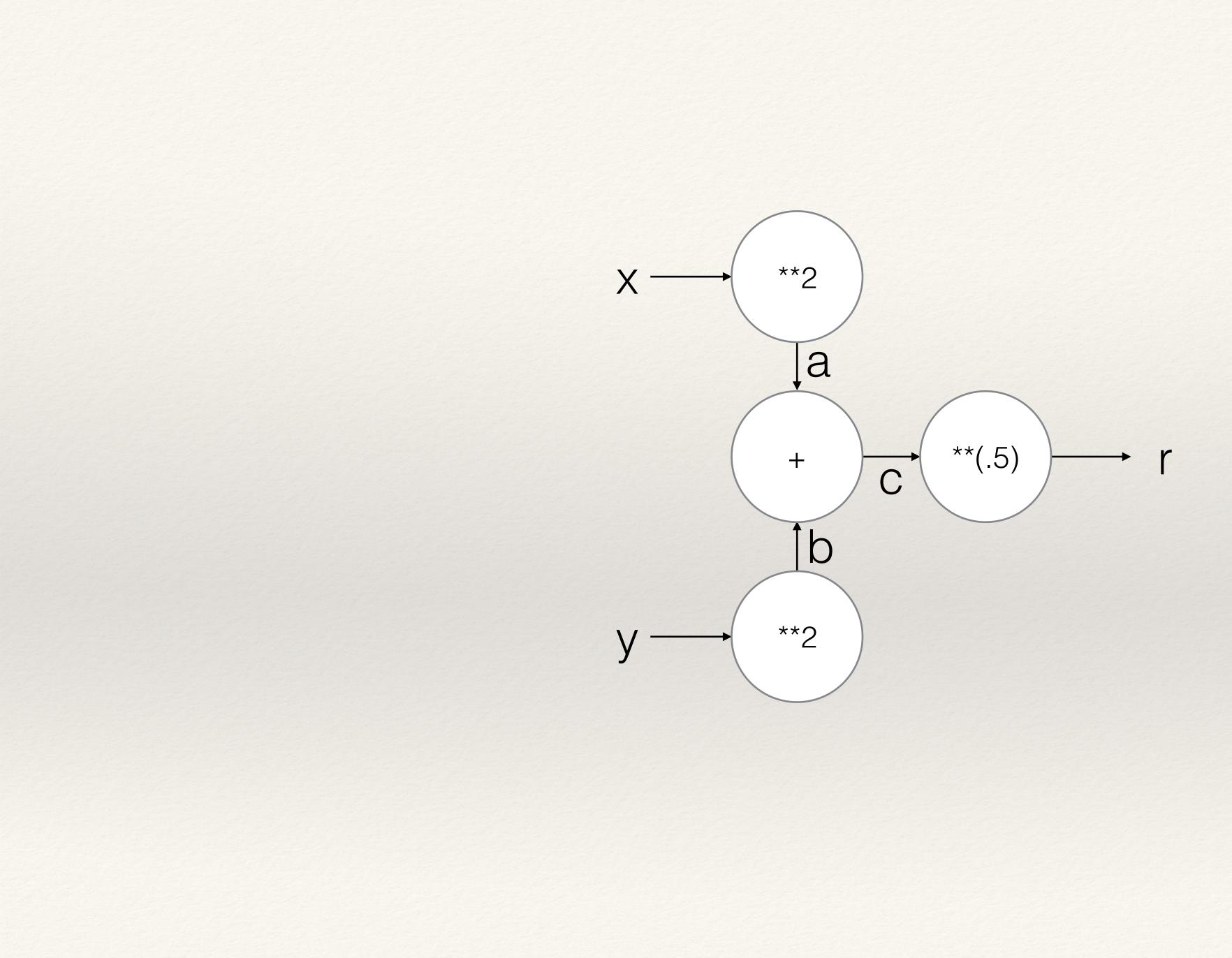

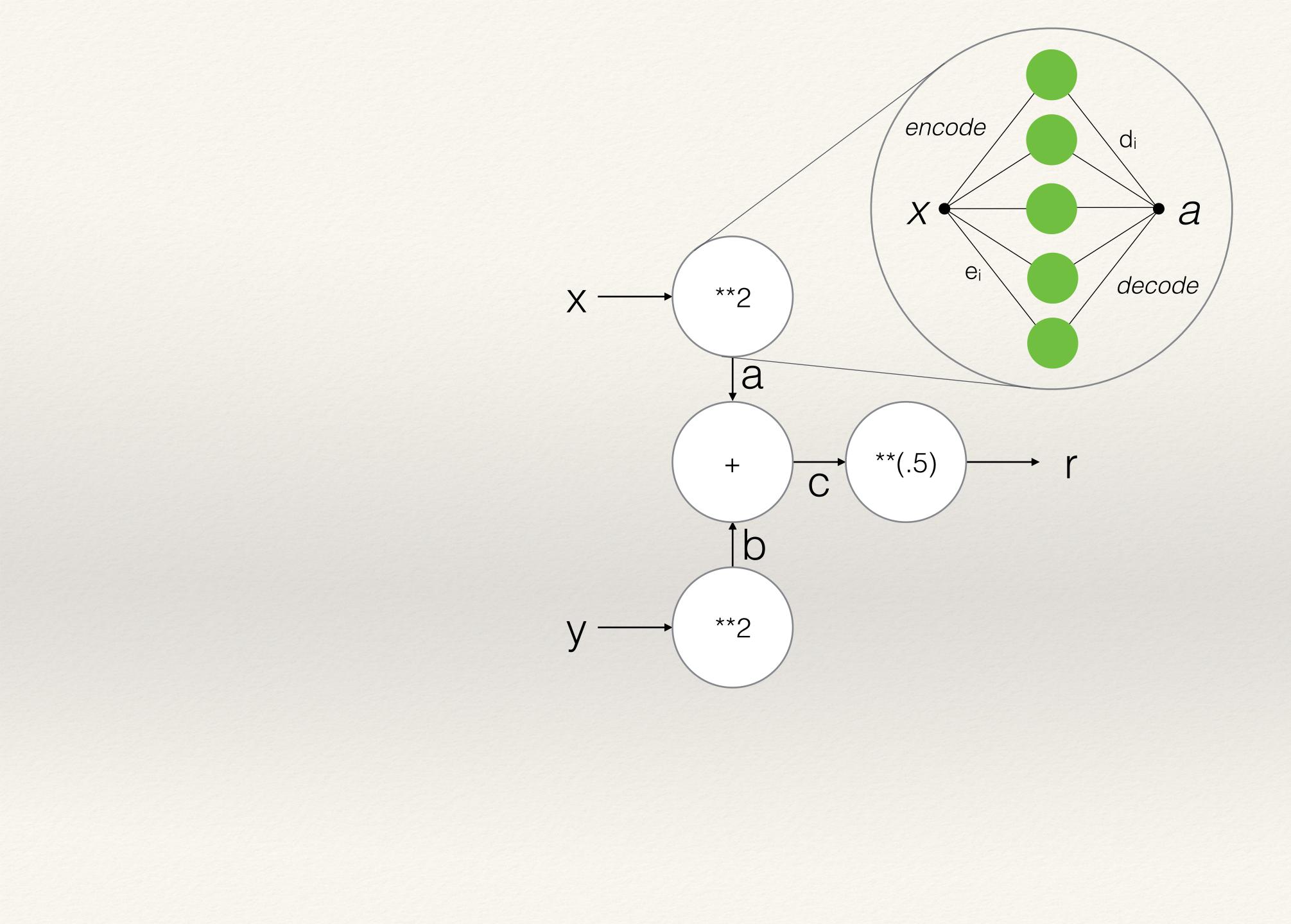

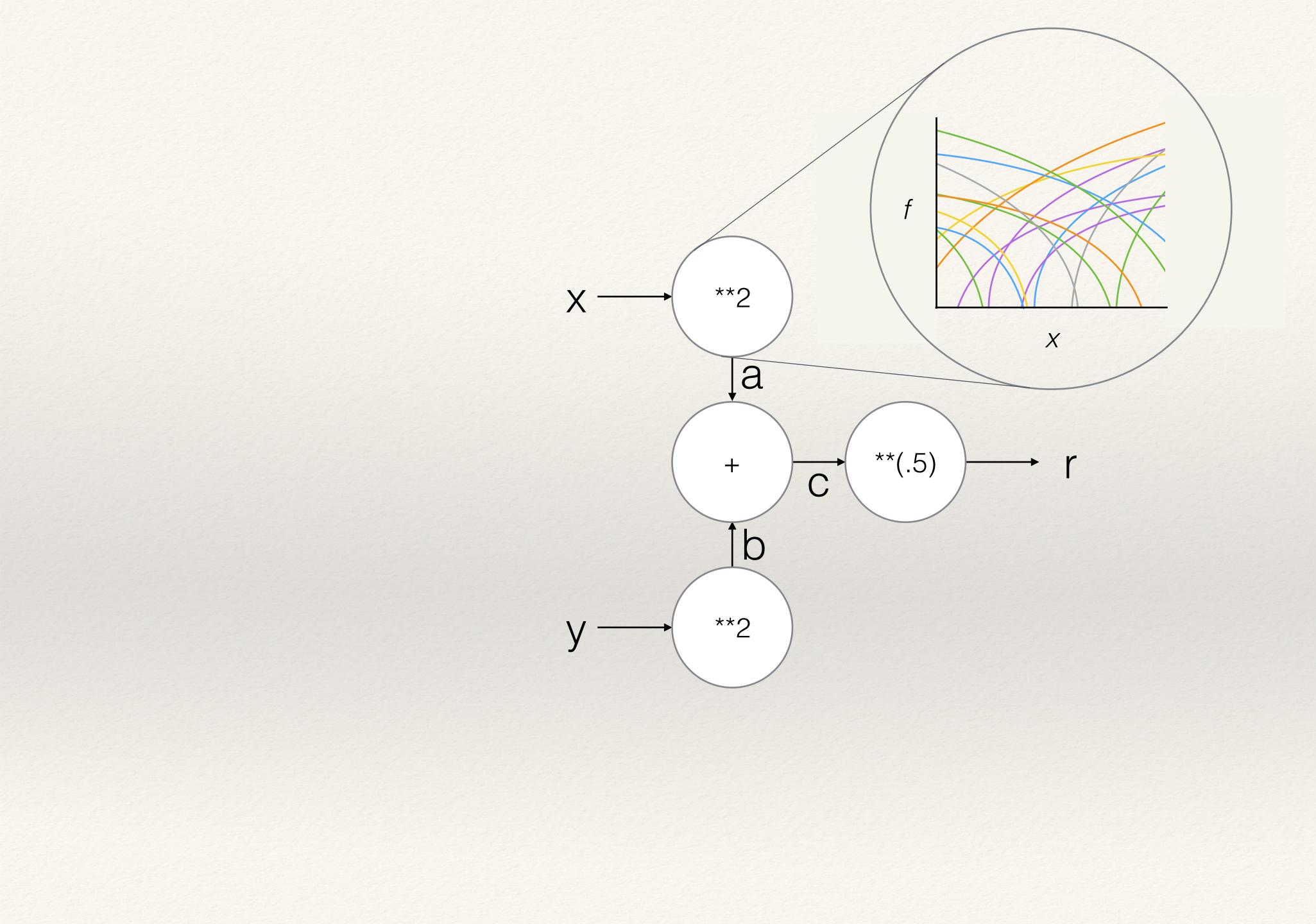

How can we unleash the computational power and energy efficiency of nanoscale transistors using analog computation and digital communication?

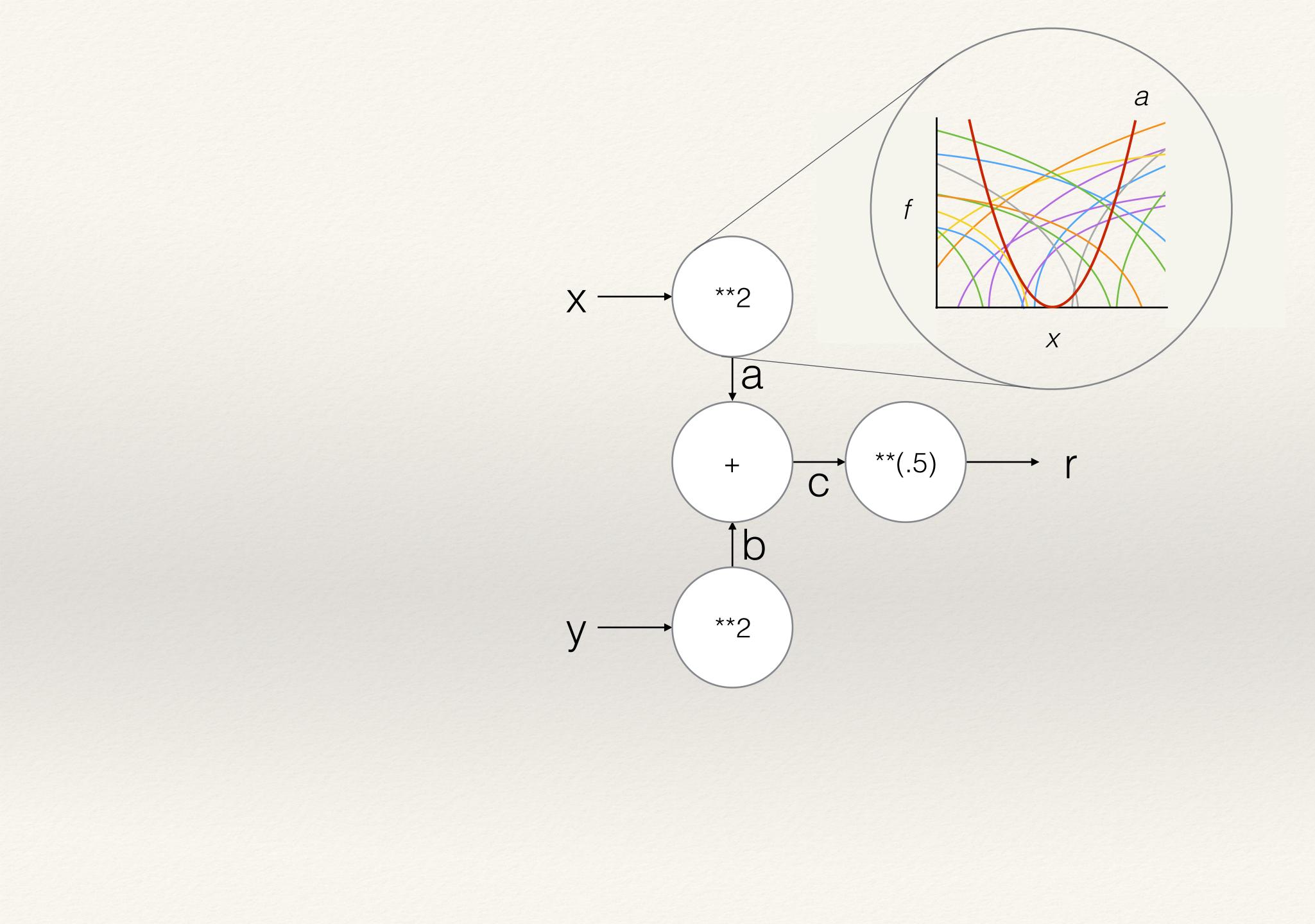

while (True):

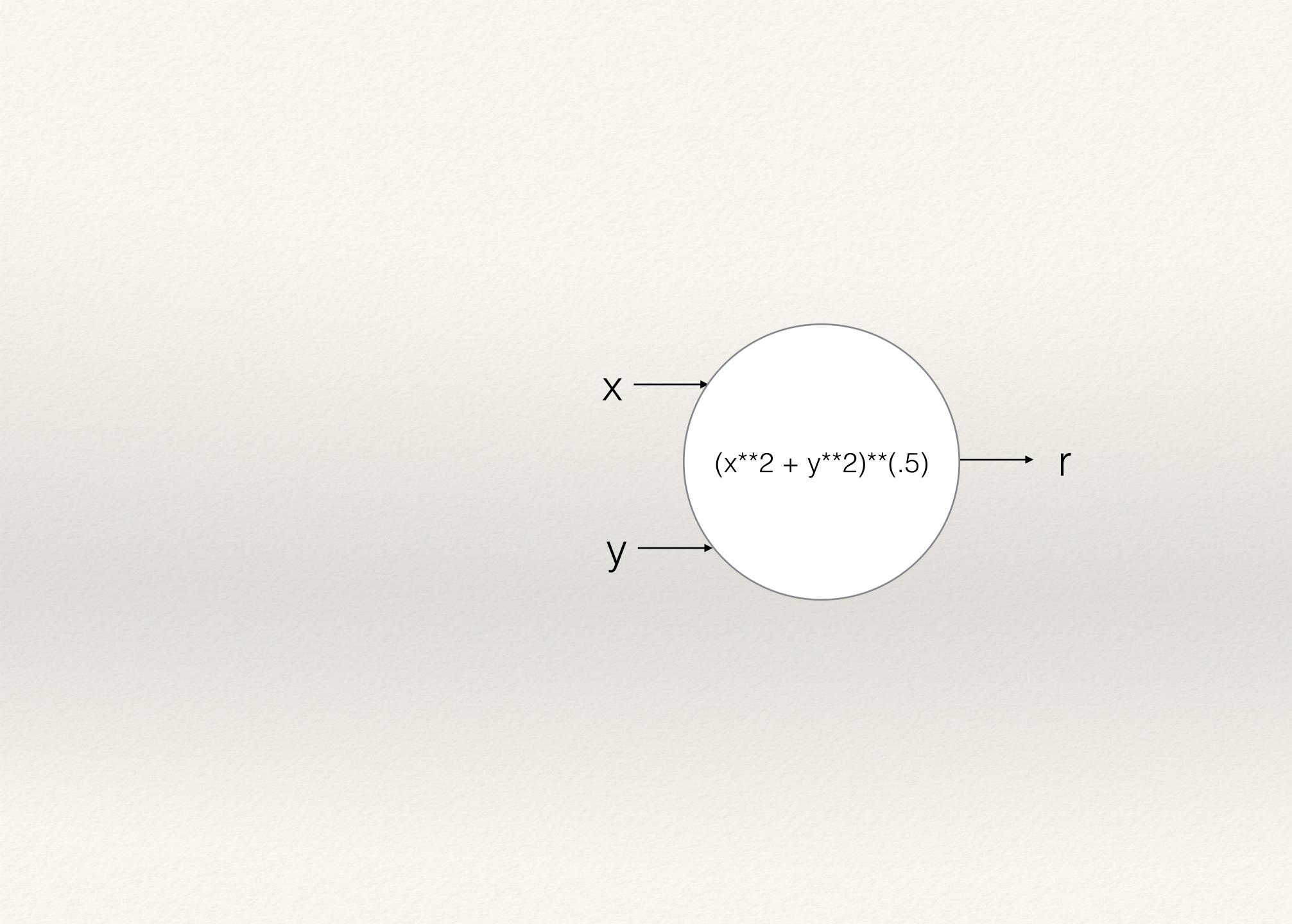

r = (x\*\*2 +

### r = (x \* \* 2 + y \* \* 2) \* \* (.5)

```

while (True):

a = x^{**2}

b = y^{**2}

c = a + b

r = c^{**}(.5)

```

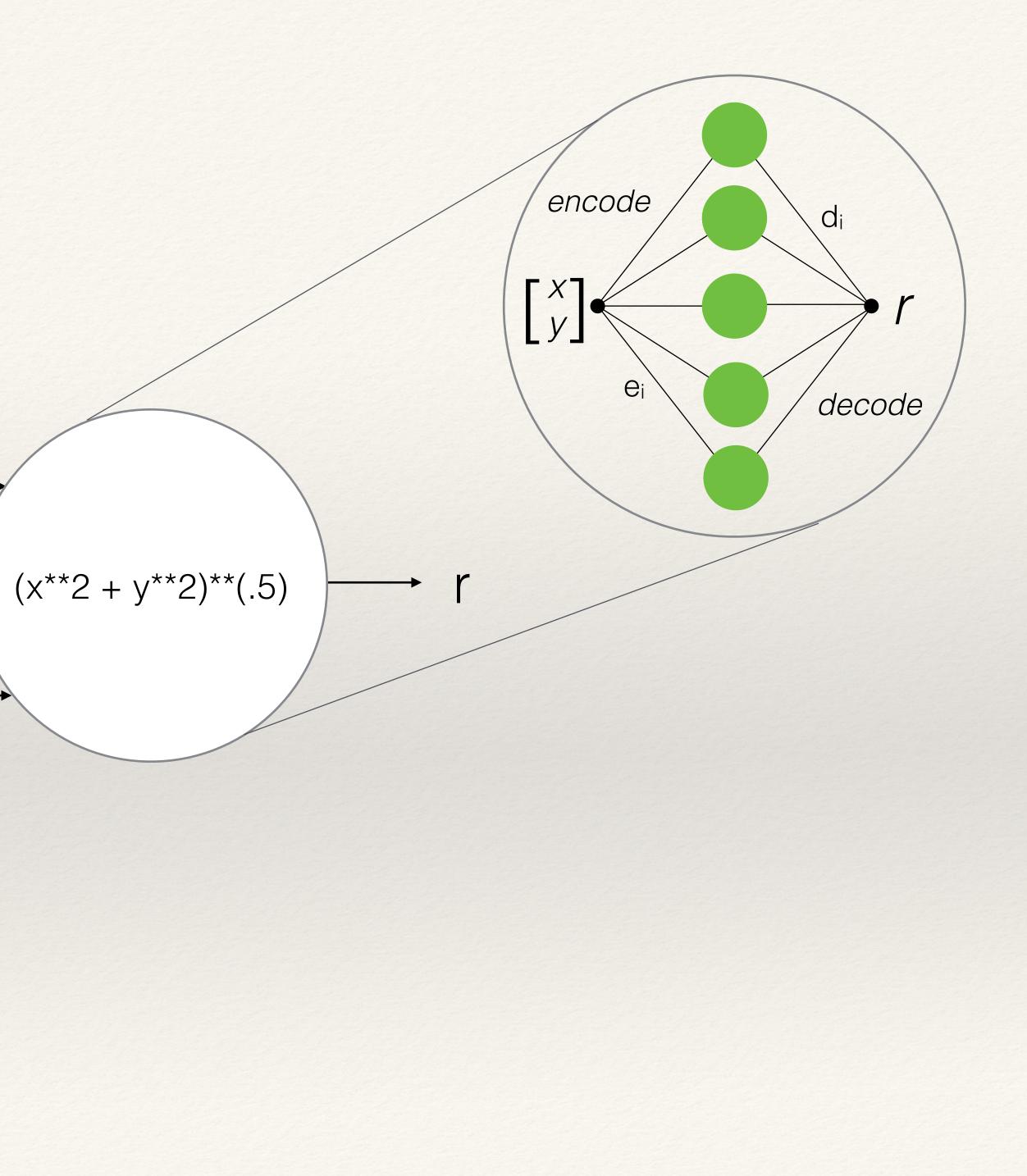

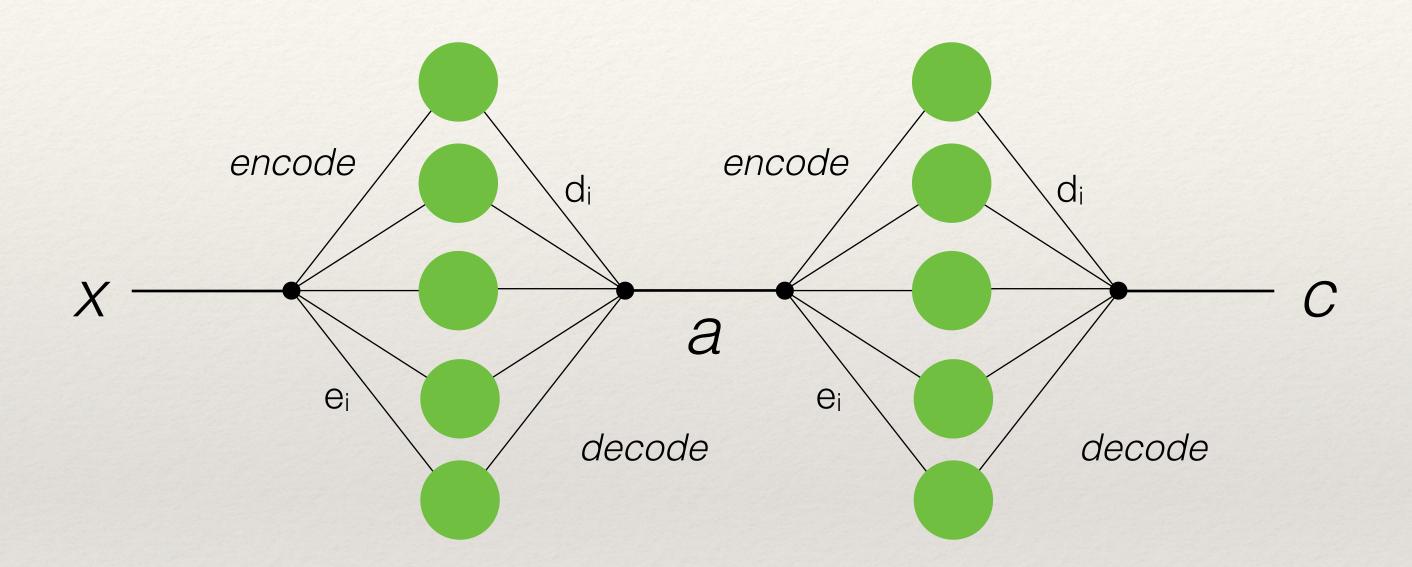

#### **Neural Engineering**

COMPUTATION, REPRESENTATION, AND DYNAMICS IN NEUROBIOLOGICAL SYSTEMS

Х

Eliasmith & Anderson 2003

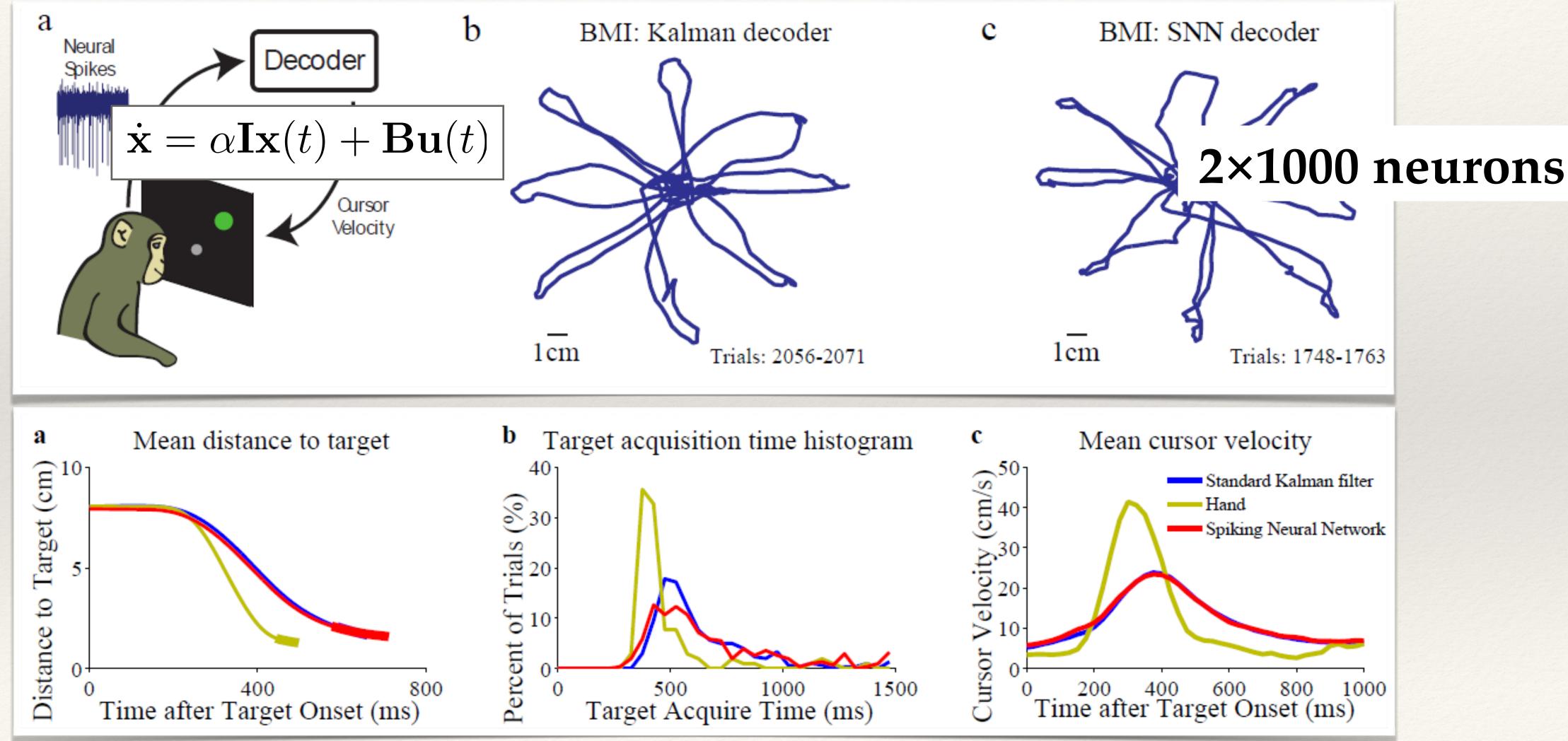

#### $\dot{\mathbf{x}} = \alpha \mathbf{I}\mathbf{x}(t) + \mathbf{B}\mathbf{u}(t)$

Courtesy of Chris Eliasmith 2013

http://www.nengo.ca

$\mathbb{V}$

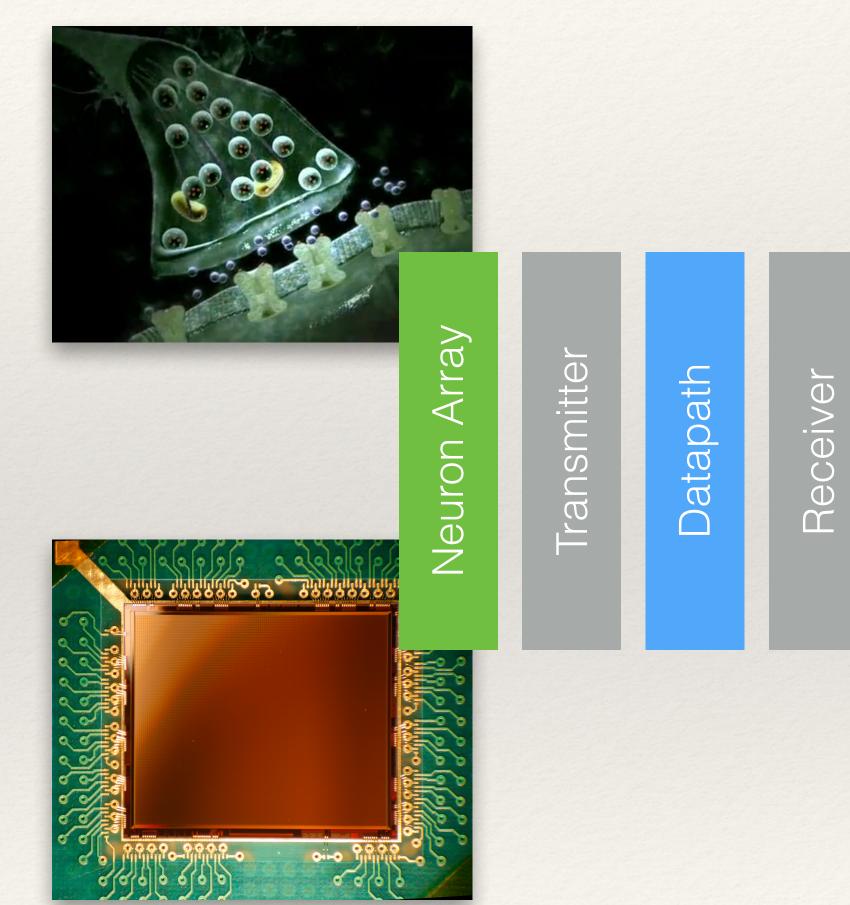

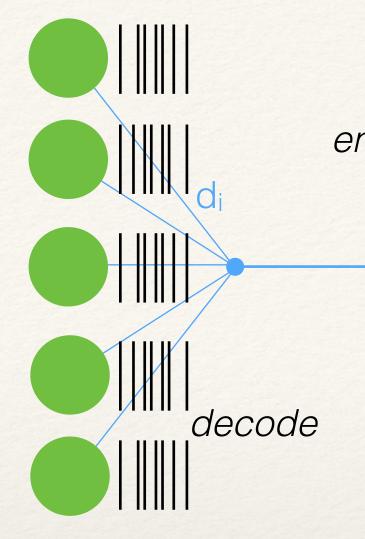

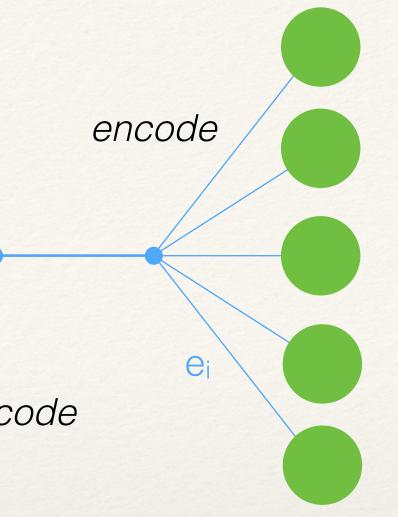

# Transmitter

Neuron Array

Router

- \* Dendrites modeled with subthreshold analog circuits

- \* Axons modeled with asynchronous digital logic

- \* Connects each neuron to thousands of others with clustered synaptic connections

- \* Real-time operation

- \* 180 nm

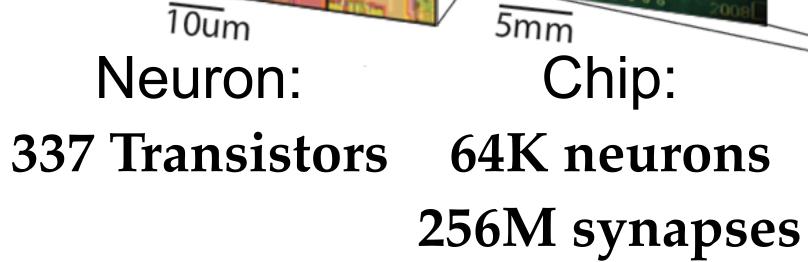

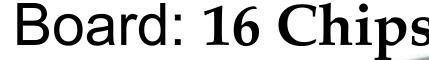

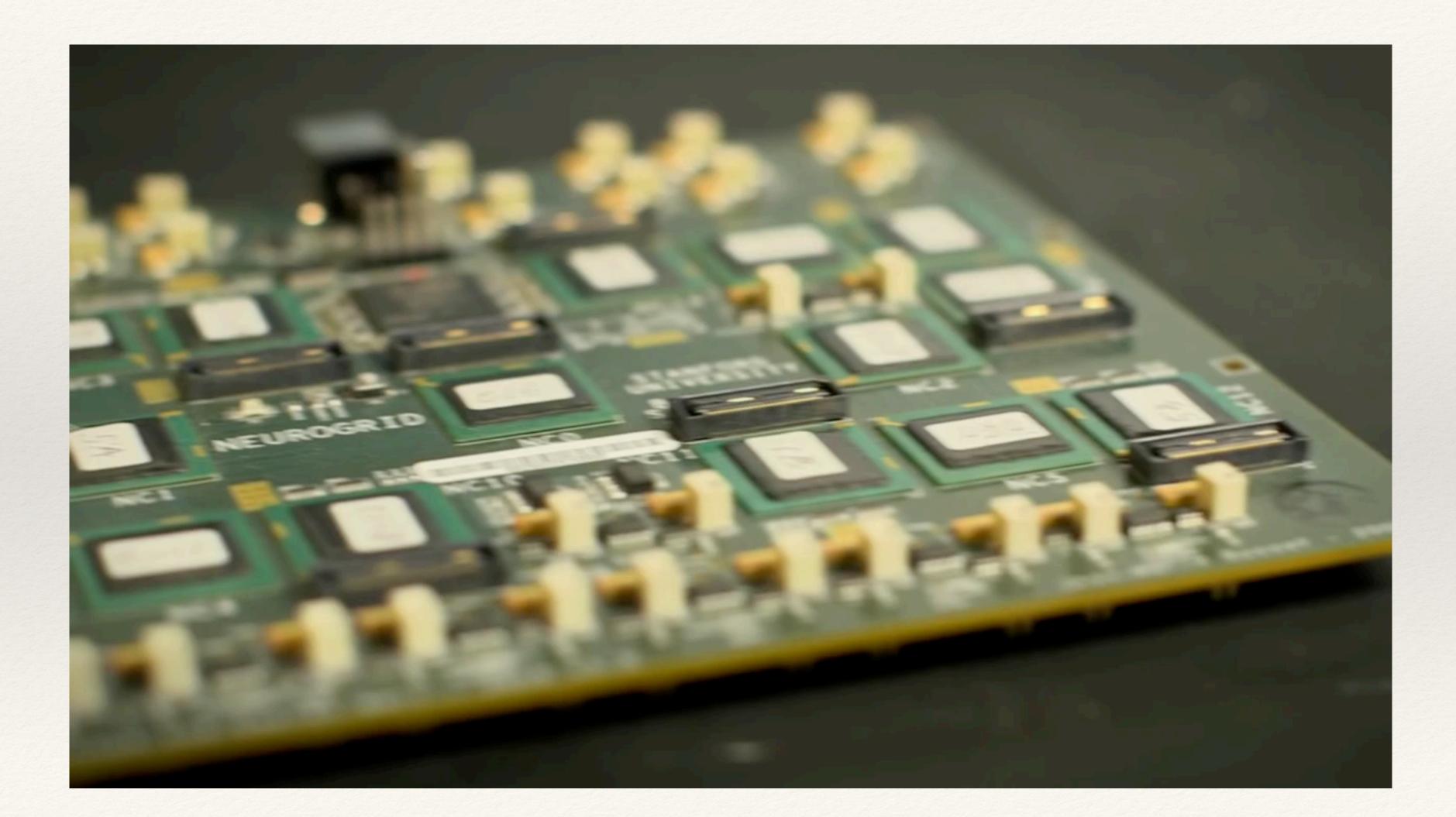

## Neurogrid

### **1M neurons** 4B synapses **3W**

Benjamin et al., 2014

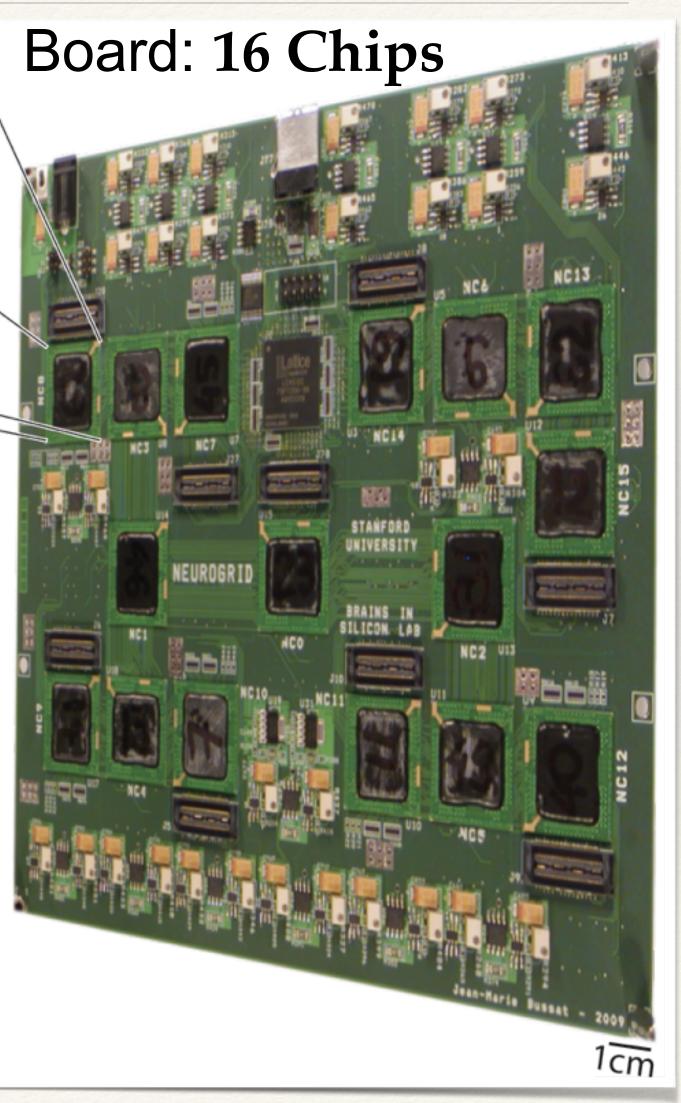

## Prosthesis power challenge

Head Mounted Electronics

**Subcutaneous Mounted Electronics**

Fully-implanted Electronics (with array)

Dethier et al. 2012

## Spiking neural network decoder

Dethier et al. 2012

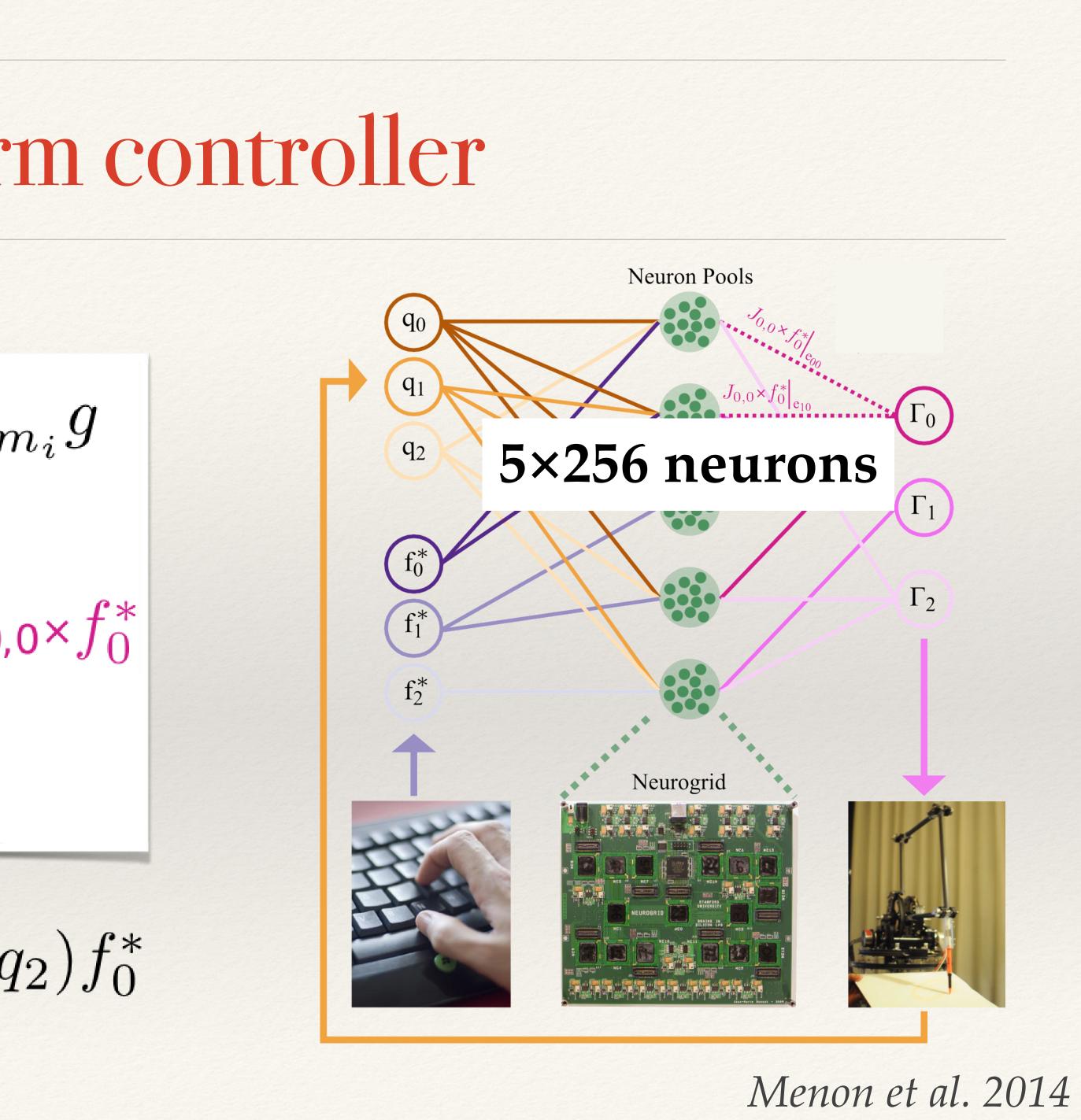

## Robot-arm controller

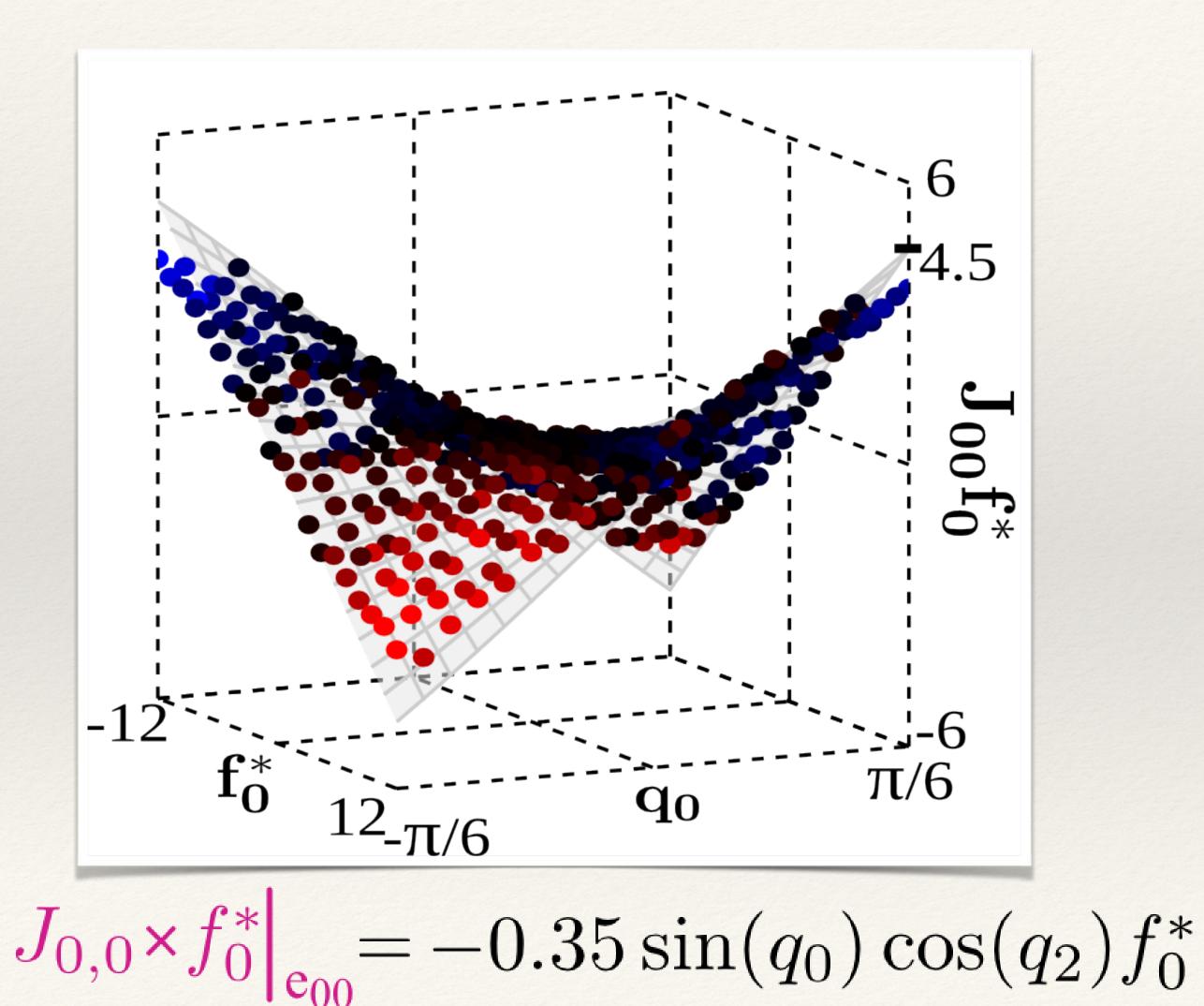

$$\Gamma = J_x^T f_x^* + \sum_{i=0}^4 m_i J_{cor}^T$$

$$\begin{bmatrix} J_{0,0} & J_{0,1} & J_{0,2} \\ J_{1,0} & J_{1,1} & J_{1,2} \\ J_{2,0} & J_{2,1} & J_{2,2} \end{bmatrix}^T \begin{bmatrix} f_0^* \\ f_1^* \\ f_2^* \end{bmatrix} \longrightarrow J_0,$$

$\left. J_{0,0} \times f_0^* \right|_{e_{00}} = -0.35 \sin(q_0) \cos(q_2) f_0^*$

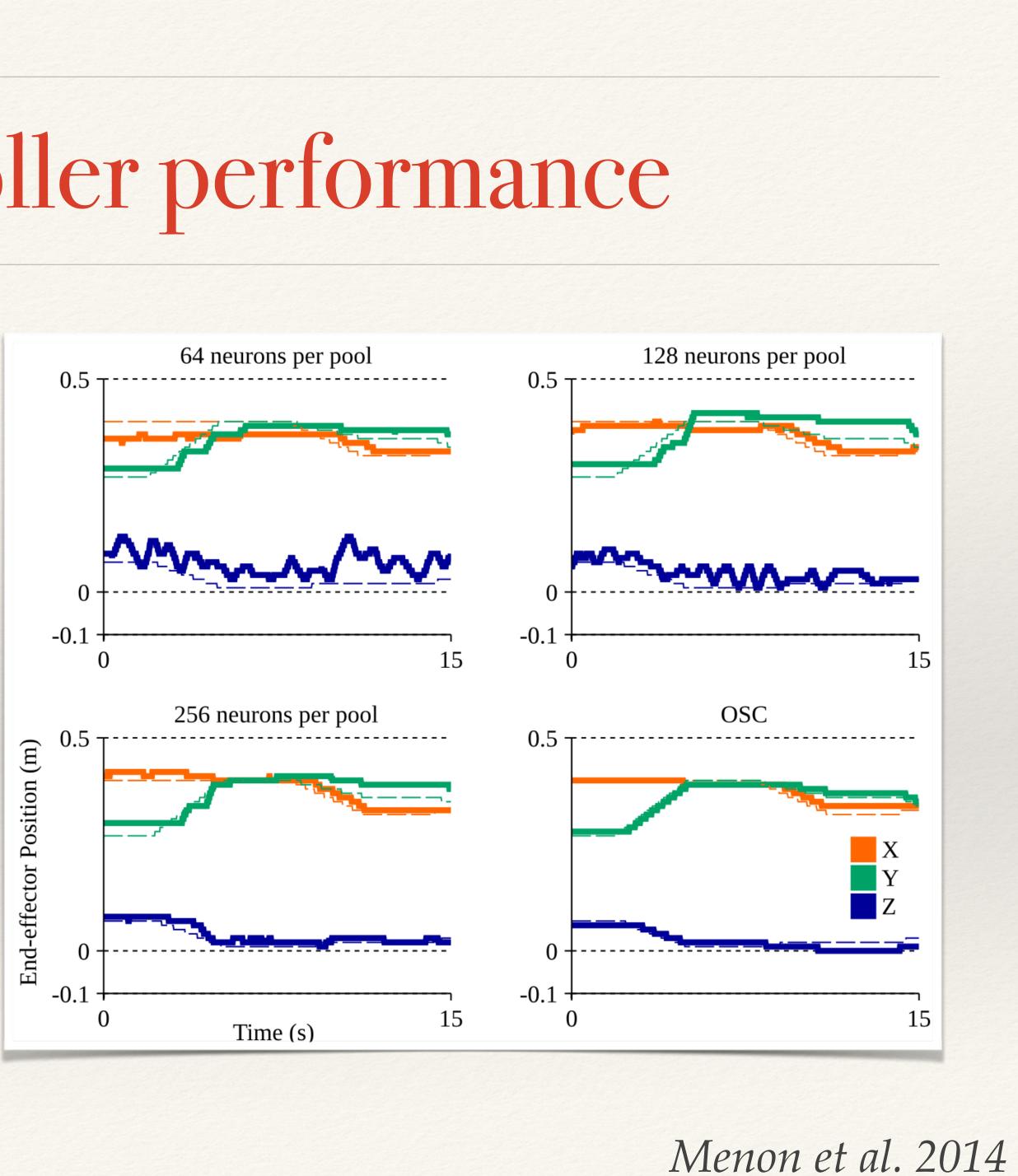

## Robot-Arm controller performance

## Robot-arm controller video

- \* Combining analog computation with digital communication proved energy-efficient and noiserobust

- \* Building the first neuromorphic chip (*Brainstorm*) that implements spiking neural networks specified at a higher level of abstraction

- \* Writing software tool (*Neuromorph*) that **automatically** synthesizes network from high-level specification

- \* **ONR**-funded collaboration with colleagues at **Cornell** and Waterloo

Summary